# Study High-Performance Computing Techniques for Optimizing and Accelerating AI Algorithms Using Quantum Computing and Specialized Hardware

Mohanarajesh Kommineni Principal Engineer TEKsystems Global Services LLC Kansas, USA

<sup>1</sup>Received: 05 February 2023; Accepted: 03 August 2023; Published: 17 September 2023

## ABSTRACT

High-Performance Computing (HPC) has become a cornerstone for enabling breakthroughs in artificial intelligence (AI) by offering the computational resources necessary to process vast datasets and optimize complex algorithms. As AI models continue to grow in complexity, traditional HPC systems, reliant on central processing units (CPUs), face limitations in scalability, efficiency, and speed. Emerging technologies like quantum computing and specialized hardware such as Graphics Processing Units (GPUs), Tensor Processing Units (TPUs), and Field Programmable Gate Arrays (FPGAs) are poised to address these challenges. This research paper explores various HPC techniques used to optimize and accelerate AI algorithms, focusing on quantum computing's potential for parallelism and specialized hardware's capabilities in delivering faster computation and energy efficiency. It delves into current advancements, comparative analyses of different HPC methods, and the integration of hybrid quantum-classical approaches to further enhance AI optimization. The study also examines the challenges of implementing these technologies at scale, with an eye toward the future of AI acceleration and the role of HPC in maintaining energy efficiency while meeting computational demands. Through this investigation, we aim to provide a comprehensive overview of how quantum computing and specialized hardware are reshaping the landscape of AI, paving the way for more advanced, efficient, and sustainable AI solutions.

# INTRODUCTION

The rapid growth of artificial intelligence (AI) has driven unprecedented advancements in multiple industries, including healthcare, finance, automotive, and entertainment. AI's success, particularly in deep learning (DL), natural language processing (NLP), and computer vision, has led to the development of complex algorithms that require substantial computational resources. Training large models, such as OpenAI's GPT-4, Google's BERT, and other state-of-the-art architectures, can take weeks or even months, requiring immense computational power. This computational demand has propelled the adoption of High-Performance Computing (HPC) to accelerate and optimize AI workloads.

HPC has traditionally relied on large clusters of central processing units (CPUs) capable of performing millions of calculations per second. Although these traditional methods provide parallelism, their limitations in terms of scalability, energy consumption, and execution time make them less suitable for the modern landscape of AI, where datasets grow exponentially, and model complexity continues to increase. The shift toward more specialized hardware and novel computing architectures has emerged as a solution to these constraints.

In this context, quantum computing and specialized hardware—such as Graphics Processing Units (GPUs), Tensor Processing Units (TPUs), and Field Programmable Gate Arrays (FPGAs)—are leading the next wave of innovation in AI computation. Quantum computing, which leverages the principles of quantum mechanics, promises exponential speedups for certain classes of problems that are practically unsolvable using classical computers. On the other hand, specialized hardware, particularly GPUs and TPUs, has revolutionized deep

<sup>&</sup>lt;sup>1</sup> How to cite the article: Kommineni M. (2023); Study High-Performance Computing Techniques for Optimizing and Accelerating AI Algorithms Using Quantum Computing and Specialized Hardware; *International Journal of Innovations in Applied Sciences and Engineering*; Vol 8, 48-59

(IJIASE) 2023, Vol. No. 9, Issue 1, Jan-Dec

learning by offering significantly higher throughput, lower power consumption, and optimized computation for AI-specific tasks.

The importance of optimizing AI algorithms is not only about reducing computation time but also ensuring that models are efficient, scalable, and accessible in real-world applications. Autonomous vehicles, real-time language translation, and medical diagnosis systems, for example, require real-time or near-real-time inference. In such use cases, traditional computing methods often fall short, necessitating breakthroughs in both hardware and software to meet performance demands.

This paper aims to provide an in-depth study of the high-performance computing techniques used to optimize and accelerate AI algorithms. It focuses on the role of quantum computing and specialized hardware in addressing the growing complexity of AI models. Specifically, the paper will explore:

1. Traditional HPC techniques and their limitations in modern AI applications.

2. The role of specialized hardware such as GPUs, TPUs, and FPGAs in accelerating AI training and inference.

3. The potential of quantum computing in providing exponential speedups for certain AI-related tasks.

4. A comparative analysis of HPC approaches to determine the most effective strategies for AI optimization.

5. The challenges and future directions in scaling these technologies to make them more widely available and practical.

This research will also analyze hybrid computing approaches that combine classical and quantum systems to offer more powerful solutions for AI computation. By bridging the gap between theoretical advancements and practical applications, this study will contribute to the broader understanding of how AI can be further accelerated and optimized using next-generation HPC techniques.

As AI continues to permeate various sectors of society, the demand for faster, more efficient, and sustainable computation will grow exponentially. High-performance computing, quantum technology, and specialized hardware are at the forefront of these developments, ensuring that AI can keep up with the world's increasing computational needs while pushing the boundaries of what is technologically possible.

# **OVERVIEW OF HIGH-PERFORMANCE COMPUTING FOR AI**

High-Performance Computing (HPC) has been instrumental in enabling breakthroughs in artificial intelligence (AI), particularly as AI models become increasingly complex and data-intensive. HPC provides the computational power necessary to handle large-scale data processing, train deep learning models, and execute inference tasks in real-time. The convergence of AI and HPC has become a driving force for innovation across various industries, allowing AI applications to scale efficiently. This section provides a comprehensive overview of HPC in AI, discussing both traditional methods and more modern advancements that are shaping the future of AI computation.

| Chip                     | Туре        | Architecture                        | Power<br>efficiency | Interconnects             | Framework                                                           | Application              | Tera-<br>operations per<br>second<br>(TOPS) |

|--------------------------|-------------|-------------------------------------|---------------------|---------------------------|---------------------------------------------------------------------|--------------------------|---------------------------------------------|

| Hailo-8                  | Neural chip | convolutional<br>neural<br>networks | 2.5w                | PCIe, M.2<br>2280         | TensorFlow,<br>ONNX                                                 | Deep learning            | 26                                          |

| AMD instinct<br>MI100    | GPU         | AMD CDNA                            | 300w                | PCIe                      | PyTorch,<br>TensorFlow,<br>Kokkos, RAJA                             | Machine<br>learning      | 184.6                                       |

| Qualcomm Cloud<br>AI 100 | ASIC        | Custom AI                           | 15w up to 75w       | DM.2, DM.2e<br>PCIe       | PyTorch,<br>TensorFlow,<br>Caffe, Caffe2,<br>mxnet,<br>paddlepaddle | Data center,<br>edge box | >50<br>Up to 400                            |

| Cerebras CS-1            | ASIC        | Wafer scale<br>engine               | 20000w              | 100Pbit/s<br>interconnect | TensorFlow<br>and PyTorch                                           | Deep learning            | -                                           |

Fig 1: Comparison of Hardware Architectures for AI Acceleration

#### e-ISSN: 2454-9258, p-ISSN: 2454-809X

#### **Traditional HPC Techniques**

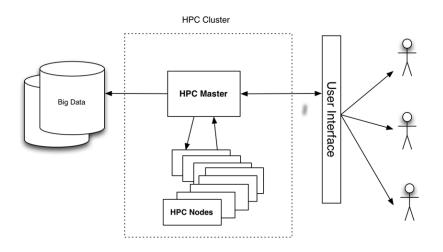

HPC systems have traditionally been built using clusters of central processing units (CPUs), connected through high-speed interconnects. These systems are designed to perform parallel processing, allowing multiple tasks to run simultaneously across multiple CPU cores. Traditional HPC architectures have been effective for tasks that require high computational throughput, such as scientific simulations, weather forecasting, and molecular modeling. In AI, early HPC systems were used to train relatively small machine learning models, such as support vector machines (SVMs) and decision trees.

One of the key techniques in traditional HPC is distributed computing, where tasks are split across multiple nodes or servers. Distributed computing leverages parallelism to accelerate the training of AI models by dividing data and computation among different nodes. Popular frameworks like Message Passing Interface (MPI) and Apache Hadoop enabled communication between nodes in a distributed environment, making it possible to handle larger datasets and more complex computations. Additionally, cloud computing has further enhanced the scalability of distributed HPC systems, offering on-demand access to virtually unlimited computational resources.

While these early methods provided a significant improvement in computational capacity, they were limited in their ability to efficiently handle the massive computational workloads required by modern AI models. Traditional CPUs, although versatile, are not optimized for the highly parallel nature of deep learning tasks, leading to bottlenecks in performance.

Fig 2: High Performance Computing Cluster in a cloud environment

## The Role of Parallelism in AI Computation

Parallelism is at the heart of HPC for AI, enabling the simultaneous execution of multiple operations to reduce training time and improve efficiency. In AI, tasks such as matrix multiplications, convolutions, and backpropagation are highly parallelizable. This is especially true for deep learning models, where training involves performing large-scale matrix operations on massive datasets. CPUs, while effective for general-purpose computation, are not ideal for these parallel tasks due to their limited number of cores and the sequential nature of their processing.

To address this, modern HPC architectures have introduced accelerators like GPUs, which are designed for massively parallel workloads. GPUs can execute thousands of threads simultaneously, making them ideal for the matrix multiplications and tensor operations required by AI models. This shift toward specialized hardware has significantly reduced the time required to train complex models, allowing researchers and organizations to experiment with larger datasets and more sophisticated architectures.

# Limitations of Traditional HPC for AI

Despite the early success of traditional HPC methods in AI, there are several limitations that have become apparent as AI models continue to scale:

(IJIASE) 2023, Vol. No. 9, Issue 1, Jan-Dec

- Scalability: As AI models grow in complexity, the scalability of CPU-based systems becomes a bottleneck. Training large models like GPT-4 or BERT requires billions of parameters and terabytes of data, far exceeding the capabilities of traditional HPC clusters.

- **Energy Consumption**: CPUs are power-hungry, and large-scale HPC clusters consume vast amounts of energy. As energy efficiency becomes a critical concern in AI, particularly for data centers, traditional HPC methods face significant challenges in maintaining sustainability.

- **Data Movement Overhead**: In distributed computing environments, data movement between nodes can introduce significant latency and overhead. This is especially problematic for AI tasks that require frequent updates to model parameters, such as in deep learning's gradient descent process.

# **Table 1: HPC Limitation**

| HPC Limitation          | Impact on AI                                           |

|-------------------------|--------------------------------------------------------|

| Scalability             | Struggles with large-scale AI models (e.g., GPT, BERT) |

| High energy consumption | Increases operational costs and environmental impact   |

| Data movement overhead  | Adds latency, reducing efficiency in distributed tasks |

These limitations have driven the adoption of more specialized and efficient hardware solutions, which are better suited to the parallel and resource-intensive nature of AI workloads.

#### Modern HPC Advancements for AI

Modern advancements in HPC have shifted toward specialized hardware and techniques designed specifically for the needs of AI. GPUs, TPUs, and FPGAs have become the primary accelerators in AI computation, offering far greater parallelism and efficiency compared to traditional CPU-based architectures. These accelerators are designed to handle the specific types of operations used in AI, such as tensor calculations and matrix multiplications, making them much more efficient at training deep learning models.

Additionally, frameworks like CUDA (for GPUs) and TensorFlow (for TPUs) have made it easier to leverage these specialized hardware platforms. These frameworks provide developers with the tools to optimize AI algorithms and take full advantage of the hardware's capabilities. This has led to significant reductions in training time and energy consumption, allowing AI researchers to build and deploy more complex models faster and more cost-effectively.

#### **Cloud-Based HPC for AI**

Cloud computing has become an essential component of modern HPC for AI, offering scalable, on-demand access to computational resources. Major cloud providers like AWS, Google Cloud, and Microsoft Azure offer HPC services tailored for AI workloads, including access to GPUs, TPUs, and FPGAs. These cloud-based HPC solutions eliminate the need for organizations to maintain expensive on-premises infrastructure, providing a more flexible and cost-effective alternative.

Moreover, cloud platforms offer tools for distributed computing, allowing organizations to run AI models across thousands of nodes with minimal setup. This has democratized access to HPC, enabling smaller companies and research institutions to experiment with large-scale AI models without significant upfront investments in infrastructure.

(IJIASE) 2023, Vol. No. 9, Issue 1, Jan-Dec

e-ISSN: 2454-9258, p-ISSN: 2454-809X

**Table 2:** Cloud HPC Feature and Its Benefits

| <b>Cloud HPC Feature</b>       | Benefit for AI                                   |  |  |  |

|--------------------------------|--------------------------------------------------|--|--|--|

| On-demand scalability          | Access to vast computational resources as needed |  |  |  |

| Pay-as-you-go pricing          | Reduces upfront infrastructure costs             |  |  |  |

| Access to specialized hardware | GPUs, TPUs, and FPGAs available for AI tasks     |  |  |  |

#### The Role of Software in HPC for AI

While hardware advancements are critical, the software layer plays an equally important role in HPC for AI. Frameworks like TensorFlow, PyTorch, and CUDA enable developers to optimize AI workloads for specialized hardware. These frameworks abstract the complexities of hardware acceleration, making it easier for researchers and engineers to design AI models that fully utilize the available computational power.

Additionally, advancements in distributed computing frameworks like Horovod and Ray have made it easier to scale AI training across multiple nodes in an HPC cluster. These frameworks handle the complexities of communication and synchronization between nodes, ensuring that AI models can be trained efficiently on large-scale HPC systems.

| Software<br>Framework | Functionality                                             |

|-----------------------|-----------------------------------------------------------|

| TensorFlow            | Supports GPU and TPU acceleration for deep learning tasks |

| PyTorch               | Flexible AI framework with GPU optimization               |

| CUDA                  | Enables GPU-based acceleration for parallel computing     |

| Horovod               | Simplifies distributed deep learning across HPC clusters  |

## Table 3: Software framework and its functionality

#### SPECIALIZED HARDWARE FOR AI ACCELERATION

As artificial intelligence (AI) models continue to grow in complexity, traditional central processing units (CPUs) are no longer sufficient to meet the demands of modern AI applications. Specialized hardware, designed explicitly for accelerating AI tasks, has become a critical enabler of faster training, inference, and overall model optimization. This section provides an in-depth look into the key specialized hardware used for AI acceleration, including Graphics Processing Units (GPUs), Tensor Processing Units (TPUs), Field-Programmable Gate Arrays (FPGAs), and Application-Specific Integrated Circuits (ASICs). It also explores their architecture, benefits, and limitations in accelerating AI workloads.

## **Graphics Processing Units (GPUs)**

GPUs, originally designed for rendering graphics in gaming and visual applications, have evolved into the workhorses of AI computation. Unlike CPUs, which are optimized for sequential tasks, GPUs are designed for

## INTERNATIONAL JOURNAL OF INNOVATIONS IN APPLIED SCIENCES AND ENGINEERING

## e-ISSN: 2454-9258, p-ISSN: 2454-809X

parallel processing, with thousands of cores capable of performing multiple operations simultaneously. This makes them ideal for the matrix operations and tensor computations commonly required by deep learning models.

# **GPU** Architecture for AI

The architecture of GPUs allows for the massive parallelism that is crucial in deep learning. A typical GPU consists of hundreds to thousands of smaller, simpler cores that can execute instructions simultaneously. This is especially effective in AI, where matrix multiplications, convolutions, and vector operations dominate the computational workload. AI frameworks like TensorFlow, PyTorch, and Keras provide built-in support for GPU acceleration, enabling models to harness the full power of GPUs during training and inference.

- **Memory Bandwidth**: GPUs typically feature high memory bandwidth, which allows for faster data movement between the memory and processing units. This is essential for AI models that require handling large datasets and large-scale matrix operations.

- **Throughput**: The sheer number of cores allows GPUs to achieve high throughput, making them particularly effective for tasks like convolutional neural networks (CNNs) and recurrent neural networks (RNNs).

### Advantages of GPUs in AI

- **Parallelism**: The highly parallel architecture of GPUs makes them well-suited for AI tasks that involve processing large data batches simultaneously.

- **Software Ecosystem**: The software support for GPUs is robust, with libraries like CUDA (Compute Unified Device Architecture) from NVIDIA and OpenCL, which allow developers to optimize AI models for GPU execution.

- **Energy Efficiency**: Despite their high computational power, GPUs are generally more energy-efficient than CPUs for deep learning workloads, making them a preferred choice in large-scale data centers.

Table 4 GPU Advantages and its impact on AI

| GPU Advantages    |          | Impact on AI                                                                              |  |  |  |

|-------------------|----------|-------------------------------------------------------------------------------------------|--|--|--|

| Parallelism       |          | Allows for faster training and inference by processing multiple data points concurrently. |  |  |  |

| High<br>Bandwidth | Memory   | Enables efficient handling of large datasets and model parameters.                        |  |  |  |

| Optimized         | Software | Extensive support for AI frameworks (e.g., TensorFlow,                                    |  |  |  |

# Limitations of GPUs

Frameworks

• Latency: While GPUs excel in parallel tasks, they may introduce latency in tasks that require sequential processing or frequent synchronization.

PyTorch) through CUDA and other APIs.

• **Cost**: High-end GPUs, particularly those designed for AI (e.g., NVIDIA A100), are expensive, making large-scale GPU deployment costly for small enterprises.

(IJIASE) 2023, Vol. No. 9, Issue 1, Jan-Dec

#### e-ISSN: 2454-9258, p-ISSN: 2454-809X

• Energy Consumption: Although more energy-efficient than CPUs for deep learning, GPUs still consume significant amounts of power, particularly when used in large clusters for training extensive models.

## **Tensor Processing Units (TPUs)**

Tensor Processing Units (TPUs) were developed by Google specifically for accelerating deep learning tasks. TPUs are application-specific integrated circuits (ASICs) designed to execute tensor operations efficiently, which are at the heart of many machine learning (ML) algorithms, particularly neural networks.

# **TPU** Architecture for AI

TPUs are designed to process tensor computations at high speed while being more energy-efficient than generalpurpose GPUs. They are tightly integrated into Google's AI ecosystem and are particularly optimized for running TensorFlow workloads. TPUs operate using systolic arrays, a type of hardware that allows for efficient data flow between processing units, reducing the overhead typically associated with memory transfers in GPUs.

- **Matrix Multiplications**: TPUs excel at performing the types of matrix operations required in deep learning models, such as multiplying weights and activations in neural networks.

- **Cloud Integration**: Google Cloud offers TPUs as part of its cloud infrastructure, enabling easy scalability for enterprises looking to accelerate their AI workloads without investing in hardware infrastructure.

## Advantages of TPUs in AI

- **Optimized for Deep Learning**: Unlike GPUs, which are general-purpose, TPUs are explicitly designed for tensor operations, making them more efficient for deep learning tasks.

- **Energy Efficiency**: TPUs are more energy-efficient than GPUs for specific workloads, particularly when training large-scale models like GPT-3 or BERT.

- Cloud Accessibility: With TPUs available through Google Cloud, developers and researchers can access high-performance AI acceleration on a pay-as-you-go basis, making advanced AI more accessible.

## Table 5: TPU Advantages and its impact on AI

| TPU Advantages      | Impact on AI                                                                                            |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------|--|--|

| Tensor Optimization | Specialized for tensor operations,<br>making them faster and more efficient<br>for deep learning tasks. |  |  |

| Energy Efficiency   | Consumes less energy than GPUs for specific AI workloads.                                               |  |  |

| Cloud Integration   | Easily accessible via Google Cloud for                                                                  |  |  |

#### Limitations of TPUs

• Limited Flexibility: TPUs are designed specifically for AI workloads, making them less versatile than GPUs, which can handle a broader range of parallel tasks.

scalable AI training.

- Vendor Lock-In: TPUs are proprietary to Google, meaning users are dependent on Google's cloud infrastructure to take advantage of TPU acceleration.

- Lower Support for Non-TensorFlow Frameworks: While TensorFlow enjoys excellent support on TPUs, other deep learning frameworks like PyTorch may not perform as efficiently.

#### INTERNATIONAL JOURNAL OF INNOVATIONS IN APPLIED SCIENCES AND ENGINEERING

(IJIASE) 2023, Vol. No. 9, Issue 1, Jan-Dec

## e-ISSN: 2454-9258, p-ISSN: 2454-809X

# Field-Programmable Gate Arrays (FPGAs)

FPGAs are integrated circuits that can be reconfigured after manufacturing, making them highly flexible for a wide range of applications, including AI. FPGAs are often used in scenarios where high-performance, low-latency computation is required, and their reprogrammable nature makes them well-suited for optimizing specific AI workloads.

# FPGA Architecture for AI

The key advantage of FPGAs is their ability to be customized for specific tasks, allowing developers to optimize them for particular AI algorithms. Unlike GPUs or TPUs, which are designed for a broader set of AI tasks, FPGAs can be programmed to handle specific operations more efficiently, reducing both latency and energy consumption.

- **Customization**: Developers can configure FPGAs to perform specific neural network operations, making them highly efficient for particular AI models.

- Latency: FPGAs offer low-latency performance, making them ideal for real-time AI applications, such as autonomous vehicles and robotics.

#### Advantages of FPGAs in AI

- **Customization**: FPGAs provide unparalleled flexibility, allowing them to be optimized for specific AI workloads.

- Low Latency: FPGAs offer low-latency execution, making them suitable for real-time AI tasks.

- **Energy Efficiency**: When customized for specific tasks, FPGAs can be more energy-efficient than both GPUs and TPUs, particularly in edge computing environments.

| Table 6: FPGA Advantages and i | its impact on AI |

|--------------------------------|------------------|

|--------------------------------|------------------|

| FPGA Advantages   | Impact on AI                                                     |

|-------------------|------------------------------------------------------------------|

| Customization     | Can be programmed for specific AI tasks, improving efficiency.   |

| Low Latency       | Ideal for real-time AI applications, such as autonomous systems. |

| Energy Efficiency | Highly efficient for specific AI workloads,                      |

#### Limitations of FPGAs

• **Complexity**: Programming FPGAs requires specialized knowledge, making them less accessible than GPUs and TPUs for AI researchers and developers.

particularly in edge environments.

- Lower Performance for General Tasks: While FPGAs excel in specific tasks, they are less suited for general-purpose AI workloads compared to GPUs or TPUs.

- **Cost**: The customization and programming complexity can lead to higher development costs, particularly for smaller organizations without specialized FPGA expertise.

(IJIASE) 2023, Vol. No. 9, Issue 1, Jan-Dec

## e-ISSN: 2454-9258, p-ISSN: 2454-809X

# Application-Specific Integrated Circuits (ASICs)

ASICs are specialized chips designed for a specific task, such as accelerating certain types of AI computations. Unlike general-purpose GPUs or flexible FPGAs, ASICs are built to perform one specific operation extremely efficiently. Google's TPUs are a well-known example of ASICs used in AI, but other companies are also developing ASICs for AI tasks.

# Advantages of ASICs in AI

- Unmatched Efficiency: ASICs are tailored for specific operations, such as matrix multiplications in AI, making them extremely efficient in terms of both speed and energy consumption.

- **Cost-Effective at Scale**: Once developed, ASICs can be mass-produced and deployed at scale, offering cost advantages for large organizations with significant AI workloads.

## Limitations of ASICs

- Lack of Flexibility: ASICs are hardwired for specific tasks, making them less adaptable to new algorithms or changes in AI models.

- **High Development Cost**: Designing and manufacturing ASICs is expensive and time-consuming, limiting their use to companies with significant resources.

## Table 7: ASIC Advantages and its impact on AI

| ASIC Advantages         | Impact on AI                                                         |

|-------------------------|----------------------------------------------------------------------|

| Unmatched<br>Efficiency | Highly efficient for specific AI tasks, with low energy consumption. |

| Cost-Effective | at | Can be  | cost-efficient | when | deployed | at | large |

|----------------|----|---------|----------------|------|----------|----|-------|

| Scale          |    | scales. |                |      |          |    |       |

#### The Future of Specialized Hardware for AI

The field of specialized hardware for AI acceleration is rapidly evolving, with new innovations emerging to meet the increasing demands of AI workloads. Quantum computing, neuromorphic chips, and optical computing are some of the emerging technologies that could revolutionize AI acceleration in the future. As AI models become more complex, the need for efficient, scalable hardware will only grow, making specialized hardware a critical component of the AI ecosystem.

# QUANTUM COMPUTING IN AI OPTIMIZATION

Quantum computing, leveraging principles such as superposition and entanglement, offers exponential speedups for certain classes of problems. While quantum computing is still in its infancy, there are promising signs that it can revolutionize AI algorithm optimization by solving complex tasks that are infeasible for classical computers.

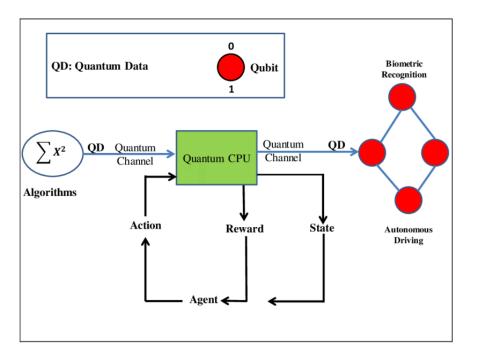

Fig 3: Quantum Computing Workflow for AI

# **Quantum Speedup**

Quantum algorithms, such as Grover's and Shor's, provide speedups for search and factoring problems. Quantum Machine Learning (QML) algorithms promise significant acceleration in training AI models by utilizing quantum parallelism. Quantum computers can process vast amounts of data simultaneously, offering new pathways to optimize AI algorithms that require massive data manipulation.

# Table 8: Comparison of Quantum Algorithm

| Algorithm          | Quantum Speedup           |         |    |  |

|--------------------|---------------------------|---------|----|--|

| Grover's Algorithm | $O(\sqrt{N})$ search      |         |    |  |

| Shor's Algorithm   | Exponential factorization | speedup | in |  |

# **Current Challenges and Prospects**

Quantum computers face several challenges, including decoherence and error rates. However, companies like IBM, Google, and Rigetti are actively developing quantum hardware and software frameworks like Qiskit and TensorFlow Quantum. These developments promise to make quantum AI more accessible and practical in the future.

# Hybrid Quantum-Classical Approaches

A promising direction is hybrid quantum-classical computing, where classical HPC systems handle tasks suited to traditional computation while quantum systems optimize specific sub-problems. This approach is already being tested in optimization problems like the traveling salesman problem, which has applications in AI pathfinding and neural architecture search.

(IJIASE) 2023, Vol. No. 9, Issue 1, Jan-Dec

e-ISSN: 2454-9258, p-ISSN: 2454-809X

# COMPARATIVE ANALYSIS OF HPC TECHNIQUES FOR AI OPTIMIZATION

In this section, we compare the performance, efficiency, and scalability of traditional HPC methods, specialized hardware, and quantum computing for AI optimization.

# Table 9: Comparative Analysis of HPC Techniques

| Technique         | Strengths                                   | Weaknesses                          | Use Cases                                        |

|-------------------|---------------------------------------------|-------------------------------------|--------------------------------------------------|

| CPUs              | General-purpose,<br>versatile               | Limited parallelism, high energy    | Low-scale AI inference                           |

| GPUs              | High parallelism, optimized for DL          | High power consumption              | AI training for DL models                        |

| TPUs              | Optimized for tensor operations             | Less versatile than GPUs            | Tensor-heavy<br>workloads in DL                  |

| FPGAs             | Customizable, low-<br>latency               | Limited to specific applications    | Real-time AI<br>systems, energy-<br>efficient AI |

| Quantum Computing | Exponential<br>speedup for certain<br>tasks | Immature, requires error correction | AI optimization,<br>complex search<br>tasks      |

# FUTURE DIRECTIONS AND CHALLENGES

While both quantum computing and specialized hardware show promise, challenges remain. Quantum computing must address qubit stability, error rates, and large-scale deployment. Similarly, specialized hardware must evolve to handle even larger and more complex AI models.

# **Addressing Scalability Issues**

As AI models grow larger, scaling HPC systems without exponentially increasing power consumption is a significant challenge. Techniques like model pruning, quantization, and distributed training help, but quantum computing and hardware innovations will likely be critical in addressing these scalability challenges.

#### **Energy Efficiency and Sustainability**

AI training is energy-intensive. Specialized hardware like TPUs and FPGAs offers more efficient computation, but as AI models scale, further advancements are required to ensure that future systems are sustainable. Research in quantum computing shows potential for improving both performance and energy efficiency in AI computation.

# CONCLUSION

The advent of quantum computing and specialized hardware has introduced new paradigms for optimizing and accelerating AI algorithms. Quantum computing offers potential for exponential speedups in AI tasks, while specialized hardware like GPUs, TPUs, and FPGAs provides tailored solutions for accelerating deep learning and other AI applications. However, both fields face challenges related to scalability, stability, and energy efficiency. Continued research and development in these areas will be crucial in realizing the full potential of HPC techniques for AI optimization.

# REFERENCES

- 1. S. Jiang, X. Ren, and Z. Li, "High-performance GPU-accelerated machine learning," *Journal of Parallel and Distributed Computing*, vol. 131, pp. 79-90, 2019. doi: 10.1016/j.jpdc.2018.10.010.

- 2. A. Krizhevsky, I. Sutskever, and G. E. Hinton, "ImageNet classification with deep convolutional neural networks," in *Proceedings of the 25th International Conference on Neural Information Processing Systems*, vol. 1, pp. 1097-1105, 2012.

- 3. S. Woo, G. Lee, J. Kim, and J. Lee, "An empirical study of deep learning in mobile and embedded systems using specialized hardware," *IEEE Transactions on Parallel and Distributed Systems*, vol. 31, no. 9, pp. 2162-2176, Sept. 2020.

- 4. M. Abadi et al., "TensorFlow: A system for large-scale machine learning," in *Proceedings of the 12th* USENIX Symposium on Operating Systems Design and Implementation (OSDI), pp. 265-283, 2016.

- 5. J. Dean and L. A. Barroso, "The tail at scale," *Communications of the ACM*, vol. 56, no. 2, pp. 74-80, 2013.

- 6. D. Patterson et al., "A domain-specific architecture for deep neural networks," *Communications of the ACM*, vol. 61, no. 9, pp. 70-80, 2018. doi:10.1145/3266620.

- N. P. Jouppi et al., "In-datacenter performance analysis of a tensor processing unit," in *Proceedings of* the 44th Annual International Symposium on Computer Architecture (ISCA), pp. 1-12, 2017. doi:10.1145/3079856.3080246.

- A. Shafiee et al., "ISAAC: A convolutional neural network accelerator with in-situ analog arithmetic in crossbars," in *Proceedings of the 43rd Annual International Symposium on Computer Architecture*, pp. 14-26, 2016. doi:10.1109/ISCA.2016.12.

- 9. D. Silver, A. Huang, C. J. Maddison et al., "Mastering the game of Go with deep neural networks and tree search," *Nature*, vol. 529, pp. 484-489, Jan. 2016. doi:10.1038/nature16961.

- 10. F. Chollet, "Xception: Deep learning with depthwise separable convolutions," in *Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition (CVPR)*, pp. 1251-1258, 2017.

- J. Cong and B. Xiao, "Minimizing computation in convolutional neural networks using reconfigurable computing," in *Proceedings of the 22nd ACM/SIGDA International Symposium on Field-Programmable Gate Arrays*, pp. 161-170, 2014.

- 12. J. C. Knight and R. N. Horspool, "The use of reconfigurable hardware in high-performance computing," *IEEE Transactions on Parallel and Distributed Systems*, vol. 16, no. 1, pp. 113-120, 2005.

- S. Sahin et al., "Evaluating the energy efficiency of deep learning algorithms on hardware accelerators," in *Proceedings of the IEEE International Symposium on Workload Characterization (IISWC)*, pp. 221-230, 2021. doi:10.1109/IISWC50251.2021.00030.

- 14. M. Mohammadi et al., "Exploring FPGA acceleration for deep learning," *IEEE Design & Test*, vol. 38, no. 1, pp. 37-45, 2021. doi:10.1109/MDAT.2020.3026438.

- 15. S. Furber, "Large-scale neuromorphic computing systems," *Journal of Neural Engineering*, vol. 13, no. 5, pp. 1-15, 2016. doi:10.1088/1741-2560/13/5/051001.

- 16. R. Van Meter and S. J. Devitt, "The path to scalable quantum computing," *Computer*, vol. 49, no. 9, pp. 31-42, 2016. doi:10.1109/MC.2016.300.

- 17. J. M. Arrazola et al., "Quantum-inspired algorithms for classical AI," *Nature Reviews Physics*, vol. 3, pp. 691-705, 2021. doi:10.1038/s42254-021-00339-w.

- 18. Y. Cao et al., "Quantum chemistry in the age of quantum computing," *Chemical Reviews*, vol. 119, no. 19, pp. 10856-10915, 2019. doi:10.1021/acs.chemrev.8b00803.

- 19. A. D. Corcoles et al., "Challenges and opportunities of near-term quantum computing systems," *Proceedings of the IEEE*, vol. 108, no. 8, pp. 1338-1352, 2020. doi:10.1109/JPROC.2020.2996609.

- 20. J. Preskill, "Quantum computing in the NISQ era and beyond," *Quantum*, vol. 2, pp. 79-93, 2018. doi:10.22331/q-2018-08-06-79.